# **Target Standard Cell Library**

- Used by Design Compiler for building a circuit

- During mapping, DC will

- Choose functionally-correct gates from this lib

- "time" the circuit using supplied timing data for these gates

- · Produced either by fab or third parties

- Often available for "free" (fab adds fee to wafer cost)

- Large set of combinational cells

- Primitive: INV,NAND, NOR, AOI, OAI, XOR, MUX, etc.

- Compound: AND,OR, ADD, etc.

- Sequential, flip-flop/latch, {positive, negative} D-type Flip-flop with {set, reset}

AEN

EE 271 Lecture 8

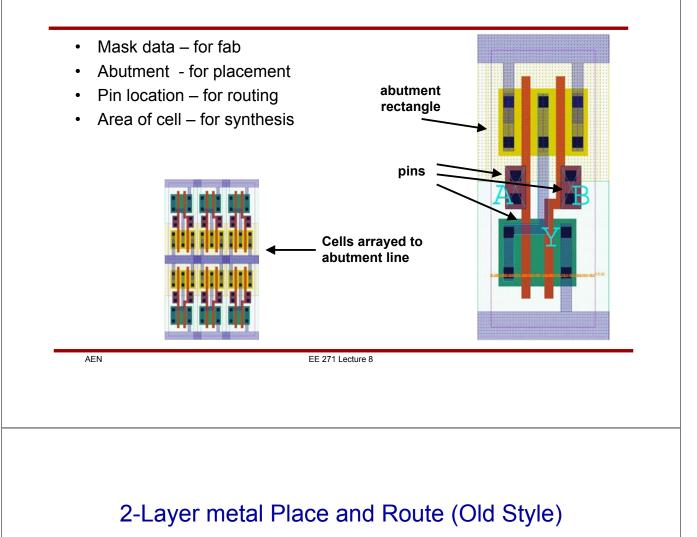

# Needed for each Cell

- Logical: relationship between outputs and inputs

- Timing/Electrical:

- Capacitance information for each pin

- Delay information for each input->output path

- Slope of outputs

- Power consumption of cell

- Required setup time for sequential cells

- Models are generally tables

- Physical:

- Layout

- Abutment and Pin location for place and rout

- Area of cell for synthesis

# Partitioning for Synthesis

- Why?

- Separate distinct functions

- Workable size and complexity

- Design reuse

- Meet physical constraints

- Good for team projects

- Bad partitioning may end up with long wires and slow design, no opt cross the boundaries

- Related CL and destination registers are grouped into one block

- Balance block size with run time

- Separate core logic, pads, clocks, ...

| AEN | EE 271 Lecture 8                                                                                             | _ |

|-----|--------------------------------------------------------------------------------------------------------------|---|

|     |                                                                                                              |   |

|     | Chip Synthesis Process                                                                                       |   |

|     | D Specification<br>HDL Description<br>HDL Description<br>Logic Level Netlist<br>Floorplan<br>Place and Route | - |

# Coding for Synthesis

- Think of topology implied by the code

- Think RTL! (Register Transfer Level)

- Writing in an RTL coding style means describing

- The register architecture

- The circuit topology

- The functionality between registers

- Design Compiler optimizes the logic in between not the register placement

AEN

#### EE 271 Lecture 8

#### Logic Synthesis Example – 4-bit Gray Counter

| <pre>module gray(clk, reset,out);</pre>                 |

|---------------------------------------------------------|

| <pre>input clk, reset;<br/>output [3:0] out;</pre>      |

| wire clk, reset;                                        |

| reg [3:0] out;                                          |

| always @(posedge clk)<br>begin                          |

| <pre>if(reset == 1) out = 4'b0000;<br/>else begin</pre> |

| end<br>end                                              |

| endmodule<br>EE 271 Lecture 8                           |

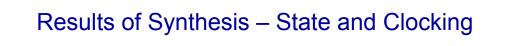

# Synthesis of Gray Counter

| <ul> <li>Use 0.13µ library</li> <li>Set clock period to 2ns</li> <li>Set clock skew to 100ps</li> <li>Set input drive equal to<br/>INVX1</li> <li>Set input arrival to be 1ns<br/>after clk</li> <li>Set output load to be 4<br/>NAND2X2 gates</li> <li>Require output valid by<br/>1ns after clock</li> </ul> | <pre>module gray(clk, reset,out);<br/>input clk, reset;<br/>output [3:0] out;<br/>wire clk,reset;<br/>reg [3:0] out;<br/>always @(posedge clk)<br/>begin</pre> |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AEN EE 2                                                                                                                                                                                                                                                                                                       | D Stark                                                                                                                                                        |  |  |  |

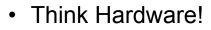

| Results of Synthesis                                                                                                                                                                                                                                                                                           |                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                |  |  |  |

| <ul> <li>Read back into schematic system after synthesis</li> </ul>                                                                                                                                                                                                                                            |                                                                                                                                                                |  |  |  |

Gate placement in schematic is somewhat random

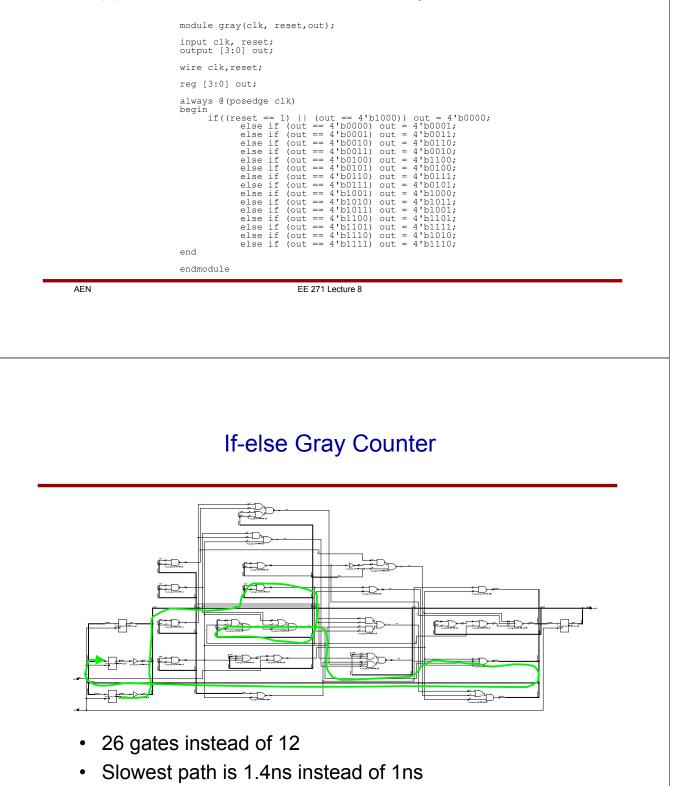

## Code Style and Synthesis Results

Suppose we make the counter this way:

# if-else Statements and case Statements

- If-else Implies multiplexing hardware

- To infer latches, use *if* without an *else* clause

- If-then-elseif statements imply priority

- Use only if priority checking is required

- Otherwise esult will be incorrect or possibly slower

- case Statements imply parallel mux function

- Use case statements where possible, particularly for FSM's

AEN

EE 271 Lecture 8

# **Combinational Adder Contents**

- 369 cell instances from 1 line of verilog

- Did you really need it?

- Tool created 32-bit Carry Lookahead Adder

- Tool contains parameterizable set of arithmetic operators

- Grabs the appropriate one for your probem

# Layout for Std Cells

- Arrange cells in rows interspersed with routing channels

- Routing runs vertically in m1, horizontally in m2

- No routing over cells

# Placement for Multiple Levels of Routing

- No need to leave channels

- Most (80-90%) of surface can be covered by cells

AEN

EE 271 Lecture 8